### DATASHEET

#### 28-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2 CONFIDENTIAL

ICSSSTUAF32868A

### Description

This 28-bit 1:2 configurable registered buffer is designed for 1.7V to 1.9V VDD operation. All inputs are compatible with the JEDEC standard for SSTL\_18, except the chip-select gate-enable (CSGEN), control (C), and reset (RESET) inputs, which are LVCMOS. All outputs are edge-controlled circuits optimized for unterminated DIMM loads, and meet SSTL\_18 specifications, except the open-drain error (QERR) output.

The ICSSSTUAF32868A operates from a differential clock (CLK and CLK). Data are registered at the crossing of CLK going high and CLK going low. The device supports low-power standby operation. When RESET is low, the differential input receivers are disabled, and undriven (floating) data, clock, and reference voltage (Vref) inputs are allowed. In addition, when **RESET** is low, all registers are reset and all outputs are forced low except QERR. The LVCMOS RESET and C inputs must always be held at a valid logic high or low level. To ensure defined outputs from the register before a stable clock has been supplied. RESET must be held in the low state during power up. In the DDR2 RDIMM application, RESET is specified to be completely asynchronous with respect to CLK and CLK. Therefore, no timing relationship can be ensured between the two. When entering reset, the register will be cleared and the data outputs will be driven low quickly, relative to the time to disable the differential input receivers. However, when coming out of reset, the register will become active guickly, relative to the time to enable the differential input receivers. As long as the data inputs are low, and the clock is stable during the time from the low-to-high transition of RESET until the input receivers are fully enabled, the design of the ICSSSTUAF32868A must ensure that the outputs will remain low, thus ensuring no glitches on the output.

The ICSSSTUAF32868A includes a parity checking function. Parity, which arrives one cycle after the data input to which it applies, is checked on the PAR\_IN input of the device. The corresponding QERR output signal for the data inputs is generated two clock cycles after the data, to which the QERR signal applies, is registered. The ICSSSTUAF32868A accepts a parity bit from the memory controller on the parity bit (PAR\_IN) input, compares it with the data received on the DIMM-independent D-inputs (D1-D5, D7, D9-D12, D17-D28 when C = 0; or D1-D12, D17-D20, D22, D24-D28 when C = 1) and indicates whether a parity error has occurred on the open-drain

QERR pin (active low). The convention is even parity, i.e., valid parity is defined as an even number of ones across the DIMM-independent data inputs combined with the parity input bit. To calculate parity, all DIMM-independent D-inputs must be tied to a known logic state. If an error occurs and the QERR output is driven low, it stays latched low for a minimum of two clock cycles or until RESET is driven low. If two or more consecutive parity errors occur, the QERR output is driven low and latched low for a clock duration equal to the parity error duration or until RESET is driven low. If a parity error occurs on the clock cycle before the device enters the low-power (LPM) and the QERR output is driven low, then it stays lateched low for the LPM duration plus two clock cycles or until RESET is driven low. The DIMM-dependent signals (DCKE0, DCKE1, DODT0, DODT1, DCS0 and DCS1) are not included in the parity check computation.

The C input controls the pinout configuration from register-A configuration (when low) to register-B configuration (when high). The C input should not be switched during normal operation. It should be hardwired to a valid low or high level to configure the register in the desired mode. The device also supports low-power active operation by monitoring both system chip select (DCS0 and DCS1) and CSGEN inputs and will gate the Qn outputs from changing states when CSGEN, DCS0, and DCS1 inputs are high. If CSGEN, DCS0 or DCS1 input is low, the Qn outputs will function normally. Also, if both DCS0 and DCS1 inputs are high, the device will gate the QERR output from changing states. If either DCS0 or DCS1 is low, the QERR output will function normally. The RESET input has priority over the  $\overline{DCS0}$  and  $\overline{DCS1}$  control and when driven low will force the Qn outputs low, and the QERR output high. If the chip-select control functionality is not desired, then the CSGEN input can be hard-wired to ground, in which case, the setup-time requirement for DCS0 and DCS1 would be the same as for the other D data inputs. To control the low-power mode with DCS0 and DCS1 only, then the CSGEN input should be pulled up to Vdd through a pullup resistor. The two VREF pins (A1 and V1) are connected together internally by approximately 150. However, it is necessary to connect only one of the two VREF pins to the external VREF power supply. An unused VREF pin should be terminated with a VREF coupling capacitor.

## **Features**

- 28-bit 1:2 registered buffer with parity check functionality

- Supports SSTL\_18 JEDEC specification on data inputs and outputs

- <u>Supports LVCMOS switching levels on CSGEN and RESET inputs</u>

- Low voltage operation: VDD = 1.7V to 1.9V

- Available in 176-ball LFBGA package

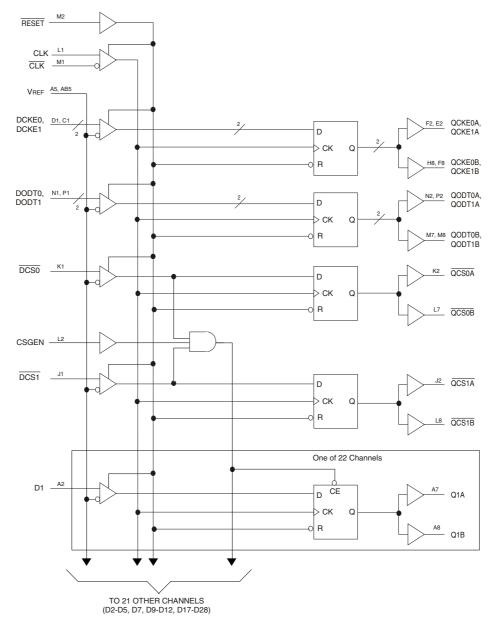

## **Block Diagram**

## **Applications**

- DDR2 Memory Modules

- Provides complete DDR DIMM solution with ICS98ULPA877A or IDTCSPUA877A

- Ideal for DDR2 400, 533, and 667

**COMMERCIAL TEMPERATURE GRADE**

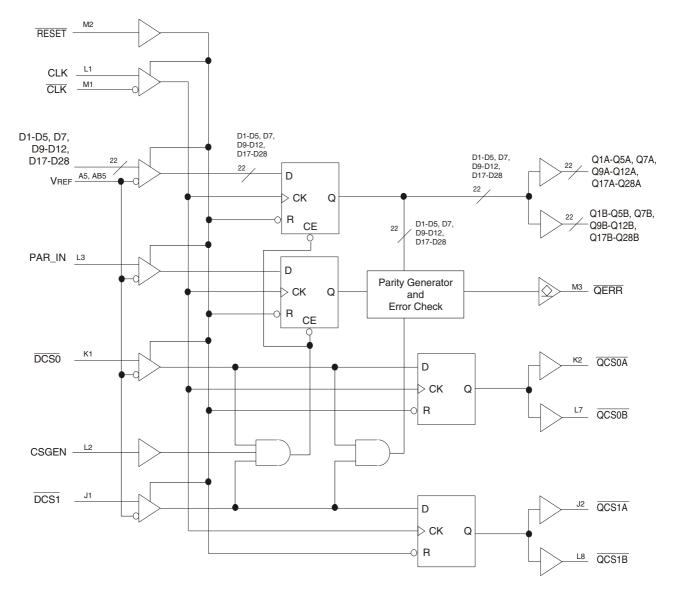

## **Parity Logic Diagram**

**COMMERCIAL TEMPERATURE GRADE**

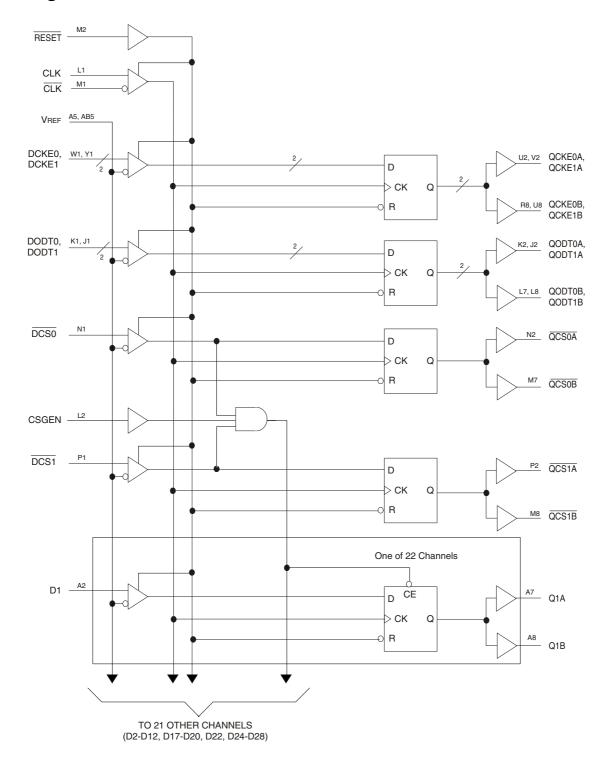

## **Block Diagram**

**COMMERCIAL TEMPERATURE GRADE**

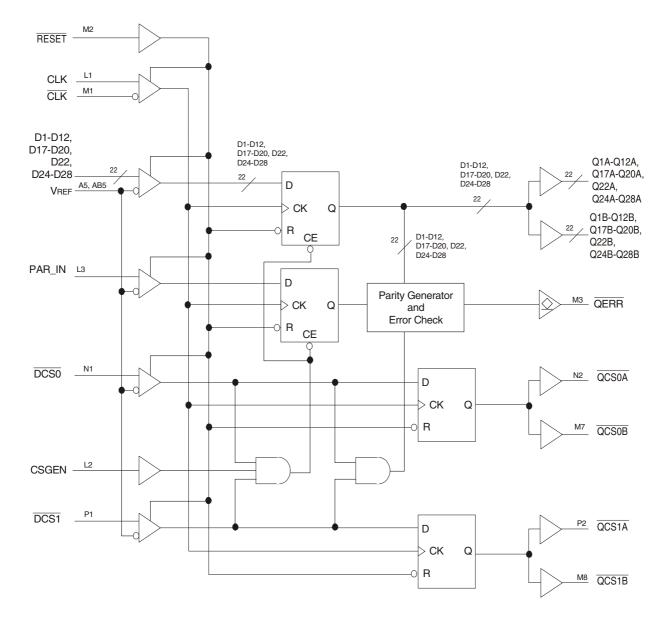

## **Parity Logic Diagram**

## Pin Configuration

|        | 1                                             | 2                                                   | 3                     | 4                                     | 5                       | 6                                             | 7                                     | 8             |

|--------|-----------------------------------------------|-----------------------------------------------------|-----------------------|---------------------------------------|-------------------------|-----------------------------------------------|---------------------------------------|---------------|

| А      | ,                                             | ,                                                   |                       | í ,<br>í                              | ( ``)                   | <u> </u>                                      | · ` ` ` ` `                           |               |

| В      | · _ ·                                         | <u>`-'</u>                                          |                       | `_'<br>/``\<br>`_'                    | `_'<br>;``,             |                                               | `-'<br>/``\<br>`-'                    |               |

| С      | <u>`-'</u>                                    | `-'<br>                                             | <u>`-'</u>            |                                       |                         |                                               | `-'<br>/``                            |               |

| D      |                                               |                                                     | · · · ·               |                                       | `'<br>                  | \'                                            |                                       |               |

|        | · · ·                                         | /``,<br>`_/                                         | /``\<br>`_'           |                                       |                         |                                               | )-\<br>\./                            |               |

| Е      | <u>,                                     </u> | <u>``</u>                                           | /``\<br>` <u>-</u> /  | )-\<br>\!                             |                         |                                               | ·-·<br>· · ·                          |               |

| F      |                                               |                                                     |                       |                                       |                         | /``,<br>`-'                                   |                                       | / ``<br>`/    |

| G      | · · ·                                         |                                                     |                       |                                       | ,-,<br>,_,              |                                               |                                       |               |

| н      |                                               | , ``,<br>`_'                                        |                       | · · · · · · · · · · · · · · · · · · · | ,                       |                                               | ,-,<br>,_;                            |               |

| J      |                                               | -<br>                                               |                       |                                       | ,-,<br>, _,             | <u>, , ,</u>                                  |                                       |               |

| к      |                                               |                                                     | · <u>-</u> /<br>/ · · |                                       |                         | · · · · · · · · · · · · · · · · · · ·         | · · · · · · · · · · · · · · · · · · · |               |

| L      |                                               |                                                     |                       |                                       |                         |                                               |                                       | <u> </u>      |

| M      | `_`<br>                                       |                                                     |                       | , - ,<br>\/<br>, - ,                  | `'                      |                                               |                                       |               |

|        |                                               | /``,<br>`_'                                         | /``,<br>`_/           |                                       |                         | <u>, , , , , , , , , , , , , , , , , , , </u> | ,-,<br>,                              |               |

| Ν      | · · · ·                                       | (``\<br>`_'                                         |                       |                                       | ,-,<br>\!               |                                               | ,-,<br>\'                             |               |

| Ρ      |                                               |                                                     |                       |                                       |                         |                                               | )-\<br>\_/                            |               |

| R      | · · ·                                         | /``,<br>`_'                                         |                       |                                       | ,<br>                   | $\sum_{i=1}^{n}$                              | ,-,<br>\!                             |               |

| т      | , ``,<br>`_`                                  | , ``.<br>`'                                         | /``\<br>` <u>-</u> /  | ·、                                    |                         |                                               | ,-,<br>`'                             |               |

| U      |                                               | -<br>`                                              | · ```                 |                                       |                         |                                               | ,-,                                   |               |

| V      |                                               | · _ /                                               |                       | · · ·                                 | , - ,<br>, - ,<br>, _ / | · · · · · · · · · · · · · · · · · · ·         | · · · · · · · · · · · · · · · · · · · |               |

|        | `_'<br>;```                                   | `-'<br>(``)                                         | `-'<br>               |                                       | ·                       |                                               |                                       | · - ·         |

| W<br>Y | `_'                                           | /``\<br>`_'                                         | /```<br>` <u>-</u> /  |                                       |                         | /``\<br>` <u>·</u> /                          | ,-,<br>,-,<br>,-,                     |               |

|        |                                               | /```,<br>`_'                                        | / ```<br>`/           |                                       |                         |                                               |                                       | / ``,<br>`_ · |

| AA     |                                               | /``.<br>`_'                                         |                       |                                       | ,,<br>                  | /``\<br>`_/                                   |                                       |               |

| AB     | /``,<br>`_'                                   | $\left( \begin{array}{c} \\ \\ \end{array} \right)$ | /``,<br>`_'           | ,-,<br>\/                             |                         | , <del>-</del> ,<br>/                         | , - `, '<br>` '                       |               |

|        |                                               |                                                     |                       |                                       |                         |                                               |                                       |               |

### 176 BALL BGA TOP VIEW

#### **COMMERCIAL TEMPERATURE GRADE**

## **Pin Configuration**

| A  | D2             | D1               | С      | GND | VREF | GND | Q1A              | Q1B              |

|----|----------------|------------------|--------|-----|------|-----|------------------|------------------|

| в  | D4             | D3               | VDD    | Vdd | VDD  | VDD | Q2A              | Q2B              |

| С  | D6<br>(DCKE1)  | D5               | GND    | GND | GND  | GND | Q3A              | Q3B              |

| D  | D8<br>(DCKE0)  | D7               | VDD    | VDD | VDD  | VDD | Q4A              | Q4B              |

| Е  | D9             | Q6A<br>(QCKE1A)  | GND    | GND | GND  | GND | Q5A              | Q5B              |

| F  | D10            | Q8A<br>(QCKE0A)  | VDD    | Vdd | Vdd  | VDD | Q7A              | Q6B<br>(QCKE0B)  |

| G  | D11            | Q10A             | GND    | GND | GND  | GND | Q9A              | Q7B              |

| н  | D12            | Q12A             | VDD    | Vdd | VDD  | VDD | Q11A             | Q8B<br>(QCKE0B)  |

| J  | DCS1           | QCS1             | GND    | GND | GND  | GND | Q10B             | Q9B              |

| к  | DCS0           | QCS0             | VDD    | VDD | VDD  | VDD | Q12B             | Q11B             |

| L  | CLK            | CSGEN            | PAR_IN | GND | GND  | GND | Q14B<br>(QCS0B)  | Q13B<br>(QCS1B)  |

| М  | CLK            | RESET            | QERR   | VDD | VDD  | VDD | Q15B<br>(QODT0B) | Q16B<br>(QODT1B) |

| Ν  | D15<br>(DODT0) | Q15A<br>(QODT0A) | GND    | GND | GND  | GND | Q17B             | Q18B             |

| Ρ  | D16<br>(DODT1) | Q16A<br>(QODT1A) | VDD    | Vdd | VDD  | VDD | Q19B             | Q20B             |

| R  | D17            | Q17A             | GND    | GND | GND  | GND | Q18A             | Q21B             |

| т  | D18            | Q19A             | VDD    | Vdd | VDD  | VDD | Q20A             | Q22B             |

| U  | D19            | Q21A             | GND    | GND | GND  | GND | Q22A             | Q23B             |

| V  | D20            | Q23A             | VDD    | Vdd | VDD  | VDD | Q24A             | Q24B             |

| w  | D21            | D22              | GND    | GND | GND  | GND | Q25A             | Q25B             |

| Y  | D23            | D24              | VDD    | VDD | VDD  | VDD | Q26A             | Q26B             |

| AA | D25            | D26              | GND    | GND | GND  | GND | Q27A             | Q27B             |

| AB | D27            | D28              | NC     | VDD | VREF | VDD | Q28A             | Q28B             |

|    | 1              | 2                | 3      | 4   | 5    | 6   | 7                | 8                |

| А  | D2             | D1               | С      | GND | VREF | GND | Q1A              | Q1B              |

|----|----------------|------------------|--------|-----|------|-----|------------------|------------------|

| в  | D4             | D3               | Vdd    | VDD | VDD  | VDD | Q2A              | Q2B              |

| С  | D6             | D5               | GND    | GND | GND  | GND | Q3A              | Q3B              |

| D  | D8             | D7               | VDD    | VDD | VDD  | VDD | Q4A              | Q4B              |

| Е  | D9             | Q6A              | GND    | GND | GND  | GND | Q5A              | Q5B              |

| F  | D10            | Q8A              | VDD    | Vdd | Vdd  | Vdd | Q7A              | Q6B              |

| G  | D11            | Q10A             | GND    | GND | GND  | GND | Q9A              | Q7B              |

| н  | D12            | Q12A             | VDD    | VDD | VDD  | VDD | Q11A             | Q8B              |

| J  | D13<br>(DODT1) | Q13A<br>(QODT1A) | GND    | GND | GND  | GND | Q10B             | Q9B              |

| К  | D14<br>(DODT0) | Q14A<br>(QODT0A) | VDD    | VDD | VDD  | VDD | Q12B             | Q11B             |

| L  | CLK            | CSGEN            | PAR_IN | GND | GND  | GND | Q14B<br>(QODT0B) | Q13B<br>(QODT1B) |

| М  | CLK            | RESET            | QERR   | Vdd | VDD  | Vdd | Q15B<br>(QCS0B)  | (QCS1B)          |

| Ν  | D15<br>(DCS0)  | Q15A<br>(QCS0A)  | GND    | GND | GND  | GND | Q17B             | Q18B             |

| Ρ  | D16<br>(DCS1)  | Q16A<br>(QCS1A)  | VDD    | VDD | VDD  | VDD | Q19B             | Q20B             |

| R  | D17            | Q17A             | GND    | GND | GND  | GND | Q18A             | Q21B<br>(QCKE0B) |

| т  | D18            | Q19A             | VDD    | VDD | VDD  | VDD | Q20A             | Q22B             |

| U  | D19            | Q21A<br>(QCKE0A) | GND    | GND | GND  | GND | Q22A             | Q23B<br>(QCKE1B) |

| V  | D20            | Q23A<br>(QCKE1A) | Vdd    | Vdd | VDD  | Vdd | Q24A             | Q24B             |

| W  | D21<br>(DCKE0) | D22              | GND    | GND | GND  | GND | Q25A             | Q25B             |

| Y  | D23<br>(DCKE1) | D24              | Vdd    | Vdd | Vdd  | Vdd | Q26A             | Q26B             |

| AA | D25            | D26              | GND    | GND | GND  | GND | Q27A             | Q27B             |

| AB | D27            | D28              | NC     | VDD | VREF | VDD | Q28A             | Q28B             |

|    | 1              | 2                | 3      | 4   | 5    | 6   | 7                | 8                |

## 1:2 REGISTER A (C = 0)

NOTE: NC denotes a no-connect (ball present but not connected to the die).

## 1:2 REGISTER B (C = 1)

## **Function Table**

|       |                  |                  | Inputs <sup>1</sup> |                  |                  |                   |         | Out                         | tputs   |                             |

|-------|------------------|------------------|---------------------|------------------|------------------|-------------------|---------|-----------------------------|---------|-----------------------------|

| RESET | DCS0             | DCS1             | CSGEN               | CLK              | CLK              | Dx, DODT,<br>DCKE | Qn      | QCS0                        | QCS1    | QODT,<br>QCKE               |

| Н     | L                | L                | Х                   | $\uparrow$       | $\downarrow$     | L                 | L       |                             |         |                             |

| Н     | L                | L                | Х                   | $\uparrow$       | $\downarrow$     | Н                 | Н       |                             |         |                             |

| Н     | L                | L                | Х                   | L or H           | L or H           | Х                 | $Q_0^2$ | $Q_0^2$                     | $Q_0^2$ | Q <sub>0</sub> <sup>2</sup> |

| Н     | L                | Н                | Х                   | $\uparrow$       | $\downarrow$     | L                 | L       |                             |         |                             |

| Н     | L                | Н                | Х                   | $\uparrow$       | $\downarrow$     | Н                 | Н       |                             |         |                             |

| Н     | L                | Н                | Х                   | L or H           | L or H           | Х                 | $Q_0^2$ | $Q_0^2$                     | $Q_0^2$ | Q <sub>0</sub> <sup>2</sup> |

| Н     | L                | L                | Х                   | $\uparrow$       | $\downarrow$     | L                 | L       |                             |         |                             |

| Н     | L                | L                | Х                   | $\uparrow$       | $\downarrow$     | Н                 | Н       |                             |         |                             |

| Н     | L                | L                | Х                   | L or H           | L or H           | Х                 | $Q_0^2$ | $Q_0^2$                     | $Q_0^2$ | Q <sub>0</sub> <sup>2</sup> |

| Н     | Н                | Н                | L                   | $\uparrow$       | $\downarrow$     | L                 | L       |                             |         |                             |

| Н     | Н                | Н                | L                   | $\uparrow$       | $\downarrow$     | Н                 | Н       |                             |         |                             |

| Н     | Н                | Н                | L                   | L or H           | L or H           | Х                 | $Q_0^2$ | $Q_0^2$                     | $Q_0^2$ | Q <sub>0</sub> <sup>2</sup> |

| Н     | Н                | Н                | Н                   | $\uparrow$       | $\downarrow$     | L                 | $Q_0^2$ |                             |         |                             |

| Н     | Н                | Н                | Н                   | $\uparrow$       | $\downarrow$     | Н                 | $Q_0^2$ |                             |         |                             |

| Н     | Н                | Н                | Н                   | L or H           | L or H           | Х                 | $Q_0^2$ | Q <sub>0</sub> <sup>2</sup> | $Q_0^2$ | Q <sub>0</sub> <sup>2</sup> |

| L     | X or<br>Floating | X or<br>Floating | X or<br>Floating    | X or<br>Floating | X or<br>Floating | X or Floating     | L       | L                           | L       | L                           |

1 H = HIGH Voltage Level

L = LOW Voltage Level

X = Don't Care

$\uparrow$  = LOW to HIGH

$\downarrow$  = HIGH to LOW

2 Output Level before the indicated steady-state conditions were established.

|       | Inputs <sup>1</sup> |                  |                  |                  |                                   |                     |                                |

|-------|---------------------|------------------|------------------|------------------|-----------------------------------|---------------------|--------------------------------|

| RESET | DCS0                | DCS1             | CLK              | CLK              | $\Sigma$ of Inputs = H (D1 - D28) | PAR_IN <sup>2</sup> | QERR <sup>3</sup>              |

| Н     | L                   | Х                | $\uparrow$       | $\downarrow$     | Even                              | L                   | Н                              |

| Н     | L                   | Х                | $\uparrow$       | $\downarrow$     | Odd                               | L                   | L                              |

| Н     | L                   | Х                | $\uparrow$       | $\downarrow$     | Even                              | Н                   | L                              |

| Н     | L                   | Х                | $\uparrow$       | $\downarrow$     | Odd                               | Н                   | Н                              |

| Н     | Х                   | L                | $\uparrow$       | $\downarrow$     | Even                              | L                   | Н                              |

| Н     | Х                   | L                | $\uparrow$       | $\downarrow$     | Odd                               | L                   | L                              |

| Н     | Х                   | L                | $\uparrow$       | $\downarrow$     | Even                              | Н                   | L                              |

| Н     | Х                   | L                | $\uparrow$       | $\downarrow$     | Odd                               | Н                   | Н                              |

| Н     | Н                   | Н                | $\uparrow$       | $\downarrow$     | Х                                 | Х                   | QERR <sub>0</sub> <sup>4</sup> |

| Н     | Х                   | Х                | $\uparrow$       | $\downarrow$     | Х                                 | Х                   | $\overline{QERR}_0$            |

| L     | X or<br>Floating    | X or<br>Floating | X or<br>Floating | X or<br>Floating | X or Floating                     | X or Floating       | Н                              |

## **Parity and Standby Function Table**

1 H = HIGH Voltage Level

L = LOW Voltage Level

X = Don't Care

$\uparrow$  = LOW to HIGH

$\downarrow$  = HIGH to LOW

2 PAR\_IN arrives one clock cycle after the data to which it applies.

3 This transition assumes  $\overline{\text{QERR}}$  is HIGH at the crossing of CLK going HIGH and  $\overline{\text{CLK}}$  going LOW. If  $\overline{\text{QERR}}$  is LOW, it stays latched LOW for two clock cycles or until  $\overline{\text{RESET}}$  is driven LOW.

4 If DCS0, DCS1, and CSGEN are driven HIGH, the device is placed in low-power mode (LPM). If a parity error occurs on the clock cycle before the device enters the LPM and the QERR output is driven LOW, it stays latched LOW for the LPM plus two clock cycles or until RESET is driven LOW.

## **Absolute Maximum Ratings**

Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

| Item                                        | Rating       |                      |  |

|---------------------------------------------|--------------|----------------------|--|

| Supply Voltage, VDD                         |              | -0.5V to 2.5V        |  |

| Input Voltage Range, VI <sup>1</sup>        |              | -0.5V to VDD + 2.5V  |  |

| Output Voltage Range, Vo <sup>1,2</sup>     |              | -0.5V to VDDQ + 0.5V |  |

| Input Clamp Current, IIK                    |              | ±50mA                |  |

| Output Clamp Current, IOK                   | ±50mA        |                      |  |

| Continuous Output Clamp Current, IO         |              | ±50mA                |  |

| Continuous Current through each VDD o       | or GND       | ±100mA               |  |

| Package Thermal Impedance $(\theta_{ja})^3$ | 0m/s Airflow | 40.4°C/W             |  |

| Tackage memai impedance (0ja)               | 1m/s Airflow | 29.1°C/W             |  |

| Storage Temperature                         | <u>.</u>     | -65 to +150°C        |  |

1 The input and output negative voltage ratings may be exceeded if the ratings of the I/P and O/P clamp current are observed.

2 This current will flow only when the output is in the high state level VO > VDDQ.

3 The package thermal impedance is calculated in accordance with JESD 51.

## **Output Buffer Characteristics**

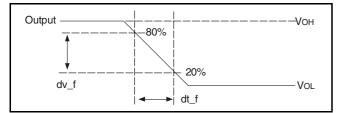

Output edge rates over recommended operating free-air temperature range

|                      | VDD = 1.8 |      |       |

|----------------------|-----------|------|-------|

| Parameter            | Min.      | Max. | Units |

| dV/dt_r              | 1         | 4    | V/ns  |

| dV/dt_f              | 1         | 4    | V/ns  |

| $dV/dt_{\Delta}^{1}$ |           | 1    | V/ns  |

1 Difference between dV/dt\_r (rising edge rate) and dV/dt\_f (falling edge rate).

## **Terminal Functions**

| Terminal Name | Electrical<br>Characteristics | Description                                                                                                                                                                                                                                                                                                                                         |

|---------------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND           | Ground Input                  | Ground                                                                                                                                                                                                                                                                                                                                              |

| Vdd           | 1.8V nominal                  | Power Supply Voltage                                                                                                                                                                                                                                                                                                                                |

| VREF          | 0.9V nominal                  | Input Reference Clock                                                                                                                                                                                                                                                                                                                               |

| CLK           | Differential Input            | Positive Master Clock Input                                                                                                                                                                                                                                                                                                                         |

| CLK           | Differential Input            | Negative Master Clock Input                                                                                                                                                                                                                                                                                                                         |

| С             | LVCMOS Input                  | Configuration Control Inputs - Register A or Register B                                                                                                                                                                                                                                                                                             |

| RESET         | LVCMOS Input                  | Asynchronous Reset Input. Resets registers and disables Vref data and clock differential-input receivers.                                                                                                                                                                                                                                           |

| CSGEN         | LVCMOS Input                  | Chip select gate enable – When high, D1-D28 inputs will be latched<br>only when at least one chip select input is low during the rising edge<br>of the clock. When low, the D1-D28 inputs will be latched and<br>redriven on every rising edge of the clock.                                                                                        |

| D1 - D28      | SSTL_18 Input                 | Data Input. Clocked in on the crossing of the rising edge of CLK and the falling edge of $\overline{\text{CLK}}$ .                                                                                                                                                                                                                                  |

| DCS0, DCS1    | SSTL_18 Input                 | Chip select inputs – These pins initiate DRAM address/command decodes, and as such at least one will be low when a valid address/command is present. The Register can be programmed to redrive all D inputs (CSGEN high) only when at least one chip select input is low. If CSGEN, DCS0, and DCS1 inputs are high, D1-D28 inputs will be disabled. |

| DCKE0, DCKE1  | SSTL_18 Input                 | The outputs of this register bit will not be suspended by the $\overline{\text{DCS0}}$ and $\overline{\text{DCS1}}$ controls                                                                                                                                                                                                                        |

| DODT0, DODT1  | SSTL_18 Input                 | The outputs of this register bit will not be suspended by the $\overline{\text{DCS0}}$ and $\overline{\text{DCS1}}$ controls                                                                                                                                                                                                                        |

| PAR_IN        | SSTL_18 Input                 | Parity Input arrives one cycle after corresponding data input                                                                                                                                                                                                                                                                                       |

| Q1 - Q28      | 1.8V CMOS                     | Data Outputs that are suspended by the $\overline{\text{DCS0}}$ and $\overline{\text{DCS1}}$ controls                                                                                                                                                                                                                                               |

| QCS0, QCS1    | 1.8V CMOS                     | Data Output that will not be suspended by the $\overline{\text{DCS0}}$ and $\overline{\text{DCS1}}$ controls                                                                                                                                                                                                                                        |

| QCKE0, QCKE1  | 1.8V CMOS                     | Data Output that will not be suspended by the $\overline{\text{DCS0}}$ and $\overline{\text{DCS1}}$ controls                                                                                                                                                                                                                                        |

| QODT0, QODT1  | 1.8V CMOS                     | Data Output that will not be suspended by the $\overline{\text{DCS0}}$ and $\overline{\text{DCS1}}$ controls                                                                                                                                                                                                                                        |

| QERR          | Open Drain Output             | Output Error bit, generated one cycle after the corresponding data output                                                                                                                                                                                                                                                                           |

| NC            |                               | No Connection                                                                                                                                                                                                                                                                                                                                       |

## **Operating Characteristics, TA = 25°C**

The RESET and Cn inputs of the device must be held at valid levels (not floating) to ensure proper device operation. The differential inputs must not be floating unless RESET is Low.

| Symbol | Parameter                    |          | Min.         | Тур.      | Max.         | Units |  |

|--------|------------------------------|----------|--------------|-----------|--------------|-------|--|

| Vdd    | I/O Supply Voltage           |          | 1.7          | 1.8       | 1.9          | V     |  |

| VREF   | Reference Voltage            |          | 0.49 * VDD   | 0.5 * Vdd | 0.51 * Vdd   | V     |  |

| Vtt    | Termination Voltage          |          | VREF - 0.04  | VREF      | VREF + 0.04  | V     |  |

| VI     | Input Voltage                |          | 0            |           | Vdd          | V     |  |

| Vih    | AC High-Level Input Voltage  | Data CSR | VREF + 0.25  |           |              |       |  |

| VIL    | AC Low-Level Input Voltage   | and      |              |           | VREF - 0.25  | V     |  |

| Vih    | DC High-Level Input Voltage  | PAR_IN   | VREF + 0.125 |           |              |       |  |

| VIL    | DC Low-Level Input Voltage   | inputs   |              |           | VREF - 0.125 |       |  |

| Vih    | High-Level Input Voltage     | RESET,   | 0.65 * VDDQ  |           |              | V     |  |

| VIL    | Low-Level Input Voltage      | C0, C1   |              |           | 0.35 * VDDQ  | V     |  |

| VICR   | Common Mode Input Range      | CLK, CLK | 0.675        |           | 1.125        | V     |  |

| Vid    | Differential Input Voltage   | ULK, ULK | 600          |           |              | mV    |  |

| Юн     | High-Level Output Current    |          |              |           | -6           | mA    |  |

| IOL    | Low-Level Output Current     |          |              | 6         | ША           |       |  |

| TA     | Operating Free-Air Temperatu | ire      | 0            |           | +70          | °C    |  |

## **DC Electrical Characteristics Over Operating Range**

Following Conditions Apply Unless Otherwise Specified:

Operating Condition: TA =  $0^{\circ}$ C to +70°C, VDDQ/VDD = 2.5V ± 0.2V.

| Symbol | Parameter                                              | Test Conditions                                                                                                                                                                                           | Min. | Тур. | Max. | Units                    |  |

|--------|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|--------------------------|--|

| Vон    | Output HIGH Voltage                                    | Юн = -6mA, VDDQ = 1.7V                                                                                                                                                                                    | 1.2  |      |      | V                        |  |

| Vol    | Output LOW Voltage                                     | IOL = 6mA, $VDDQ = 1.7V$                                                                                                                                                                                  |      |      | 0.5  | V                        |  |

| lı∟    | All Inputs                                             | VI = VDD or GND; VDD = 1.9V                                                                                                                                                                               | -5   |      | +5   | μA                       |  |

|        | Static Standby                                         | $IO = 0, VDD = 1.9V, \overline{RESET} = GND$                                                                                                                                                              |      |      | 200  | μA                       |  |

| IDD    | Statia Operating                                       | IO = 0, VDD = 1.9V, $\overline{\text{RESET}}$ = VDD, VI = VIH(AC) or VIL(AC), CLK = $\overline{\text{CLK}}$ = VIH(AC) or VIL(AC)                                                                          |      | 10   |      |                          |  |

|        | Static Operating                                       | IO = 0, VDD = 1.9V, $\overline{\text{RESET}}$ = VDD, VI = VIH(AC) or VIL(AC), CLK = VIH(AC), $\overline{\text{CLK}}$ = VIL(AC)                                                                            |      | 200  |      | - mA                     |  |

|        | Dynamic Operating<br>(clock only)                      | IO = 0, VDD = 1.8V, $\overline{\text{RESET}}$ = VDD, VI = VIH(AC) or VIL(AC), CLK and $\overline{\text{CLK}}$ switching 50% duty cycle                                                                    |      | 260  |      | μΑ/Clock<br>MHz          |  |

| Iddd   | Dynamic Operating<br>(per each data input)<br>1:2 mode | IO = 0, VDD = 1.8V, $\overline{\text{RESET}}$ = VDD, VI = VIH(AC) or VIL(AC), CLK and $\overline{\text{CLK}}$ switching 50% duty cycle. One data input switching at half clock frequency, 50% duty cycle. |      | 75   |      | μA/Clock<br>MHz/<br>Data |  |

|        | Data Inputs                                            | $VI = VREF \pm 250mV$                                                                                                                                                                                     | 2    |      | 3.5  |                          |  |

| Сі     | CLK and CLK                                            | VICR = 0.9V, VIPP = 600mV                                                                                                                                                                                 | 2.5  |      | 4    | pF                       |  |

|        | RESET                                                  | VI = VDD or GND                                                                                                                                                                                           |      | 5    |      |                          |  |

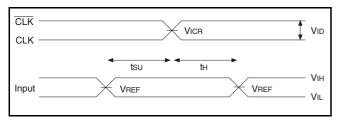

# Timing Requirements Over Recommended Operating Free-Air Temperature Range

|                       |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | VDD = 1.8 | 8V ± 0.1V |       |  |

|-----------------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------|-------|--|

| Symbol                | Parame        | ter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Min.      | Max.      | Units |  |

| <b>f</b> CLOCK        | Clock Fre     | equency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           | 410       | MHz   |  |

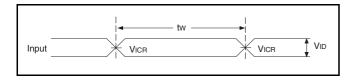

| tw                    | Pulse Du      | ration, CLK, CLK HIGH or LOW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1         |           | ns    |  |

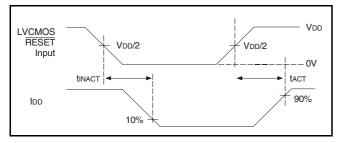

| tACT <sup>1,2</sup>   | Differenti    | ck Frequency410se Duration, CLK, CLK HIGH or LOW1erential Inputs Active Time10erential Inputs Inactive Time15 $DCS0$ before CLK $\uparrow$ , $CLK \downarrow$ , $DCS1$ and CSGEN HIGH;<br>$DCS1$ before CLK $\uparrow$ , $CLK \downarrow$ , $DCS0$ and CSGEN HIGH;<br>$DCS1$ before CLK $\uparrow$ , $CLK \downarrow$ , $DCS1$ LOW and CSGEN<br>HIGH or LOW; $DCS1$ before CLK $\uparrow$ , $CLK \downarrow$ , $DCS0$<br>LOW and CSGEN HIGH or LOW0.5 $DODTn, DCKEn, PAR_IN, and data before CLK\uparrow, CLK \downarrow0.50.5oldDCSn, DODT, n DCKEn, and data after CLK\uparrow, CLK \downarrow0.5$ |           |           |       |  |

| tinact <sup>1,3</sup> | Differenti    | al Inputs Inactive Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           | 15        | ns    |  |

|                       |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0.7       |           | ns    |  |

| ts∪                   | Setup<br>Time | HIGH or LOW; $\overline{\text{DCS1}}$ before CLK <sup>↑</sup> , $\overline{\text{CLK}}\downarrow$ , $\overline{\text{DCS0}}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0.5       |           | ns    |  |

|                       |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0.5       |           | ns    |  |

| tн                    | Hold          | $\overline{\text{DCSn}}$ , DODT,n DCKEn, and data after CLK <sup>↑</sup> , $\overline{\text{CLK}}\downarrow$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0.5       |           | ns    |  |

| LH IH                 | Time          | PAR_IN after CLK $\uparrow$ , $\overline{CLK}\downarrow$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0.5       |           | ns    |  |

1 This parameter is not production tested.

2 VREF must be held at a valid input voltage level and data inputs must be held at valid voltage levels for a minimum time of tACT (max) after RESET is taken HIGH.

3 VREF data and clock inputs must be held at valid input voltage levels (not floating) for a minimum time of tINACT (max) after RESET is taken LOW.

# Switching Characteristics Over Recommended Free Air Operating Range (unless otherwise noted)

|                |                                                                                                                | VDD = 1.3 | 8V ± 0.1V |       |

|----------------|----------------------------------------------------------------------------------------------------------------|-----------|-----------|-------|

| Symbol         | Parameter                                                                                                      | Min.      | Max.      | Units |

| fMAX           | Max Input Clock Frequency                                                                                      | 410       |           | MHz   |

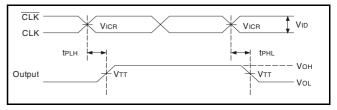

| tPDM           | Propagation Delay, single bit switching, CLK $\uparrow$ to $\overline{\text{CLK}}\downarrow$ to Qn             | 1.3       | 1.9       | ns    |

| <b>t</b> PDMSS | Propagation Delay, simultaneous switching, CLK $\uparrow$ to $\overline{\text{CLK}} \downarrow$ to Qn          |           | 2         | ns    |

| t∟H            | LOW to HIGH Propagation Delay, CLK $\uparrow$ to $\overline{\text{CLK}}\downarrow$ to $\overline{\text{QERR}}$ | 1.2       | 3         | ns    |

| tHL            | HIGH to LOW Propagation Delay, CLK $\uparrow$ to $\overline{\text{CLK}}\downarrow$ to $\overline{\text{QERR}}$ | 1         | 2.4       | ns    |

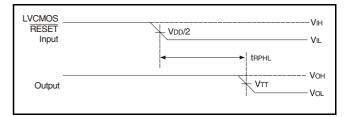

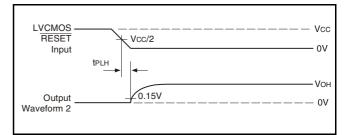

| tPLH           | HIGH to LOW Propagation Delay, $\overline{RESET}\downarrow$ to $Qn\downarrow$                                  |           | 3         | ns    |

| tPHL           | LOW to HIGH Propagation Delay, $\overline{\text{RESET}}\downarrow$ to $\overline{\text{QERR}}\uparrow$         |           | 3         | ns    |

**COMMERCIAL TEMPERATURE GRADE**

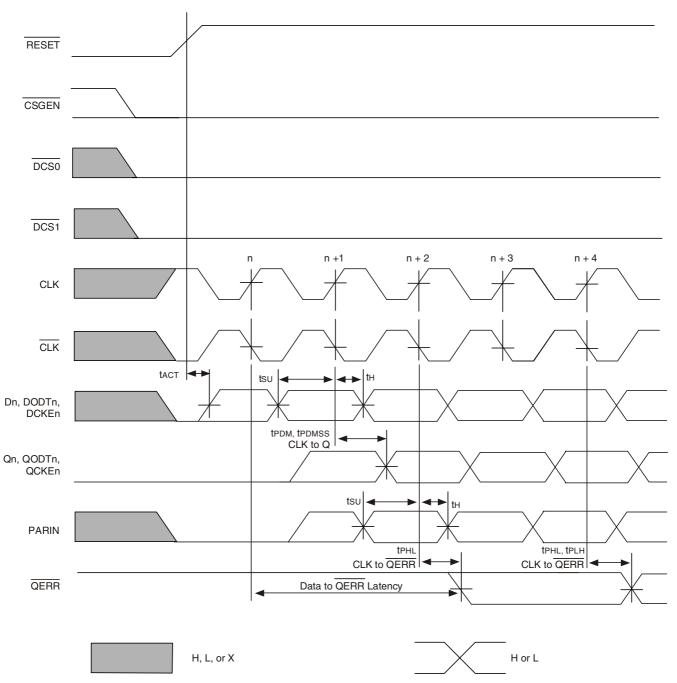

## **Register Timing**

#### NOTES:

1.After RESET is switched from LOW to HIGH, all data and PAR\_IN inputs signals must be set and held LOW for a minimum time of tACTMAX, to avoid false error.

2. If the data is clocked in on the n clock pulse, the  $\overline{\text{QERR}}$  output signal will be generated on the n+2 clock pulse, and it will be valid on the n+3 clock pulse.

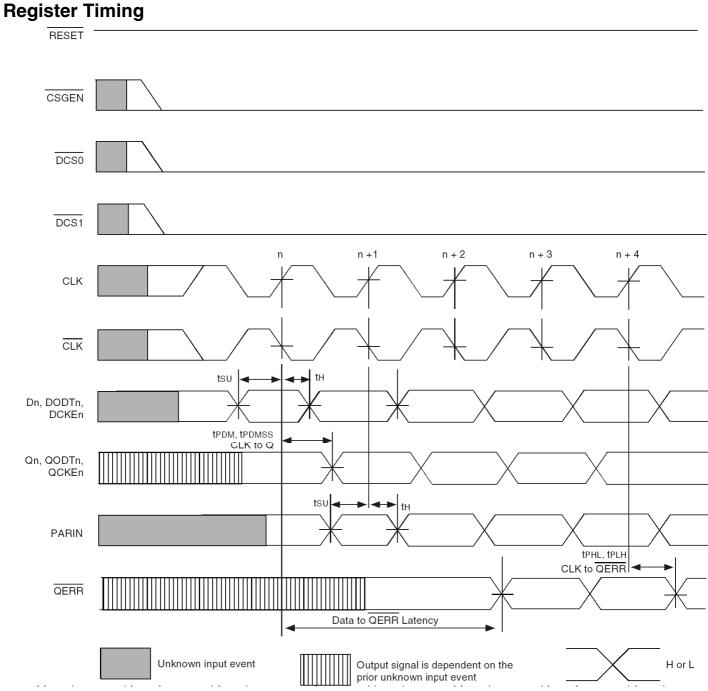

**COMMERCIAL TEMPERATURE GRADE**

#### NOTE:

1. If the data is clocked in on the n clock pulse, the QERR output signal will be generated on the n+2 clock pulse, and it will be valid on the n+3 clock pulse. If an error occurs and the QERR output is driven LOW, it stays latched LOW for a minimum of two clock cycles or until RESET is driven LOW.

**COMMERCIAL TEMPERATURE GRADE**

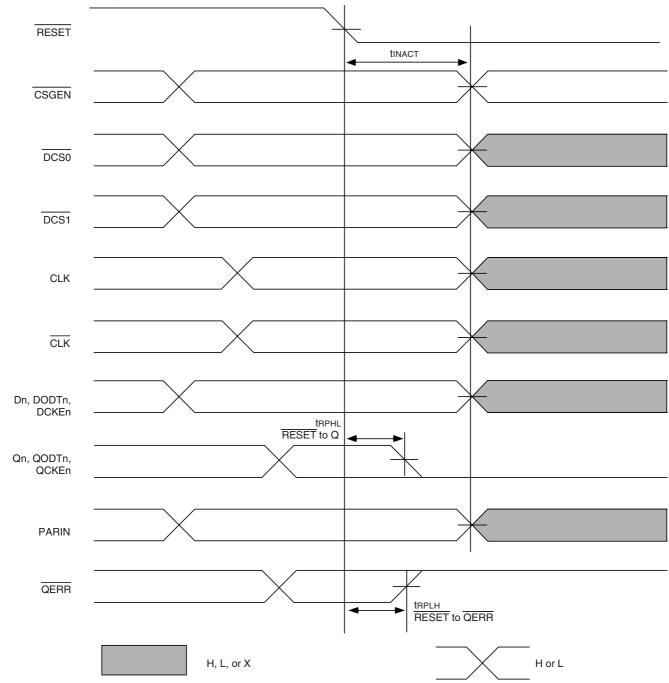

## **Register Timing**

#### NOTE:

1.After RESET is switched from LOW to HIGH, all data and clock inputs signals must be set and held at valid logic levels (not floating) for a minimum time of tINACTMAX.

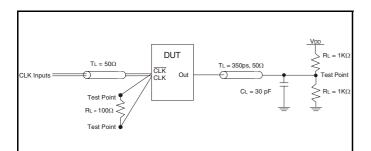

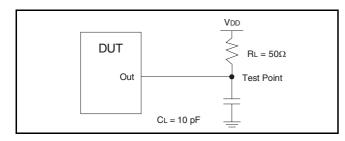

## Test Circuits and Waveforms ( $VDD = 1.8V \pm 0.1V$ )

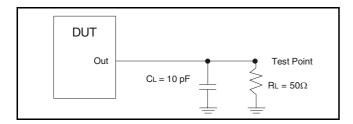

#### **Simulation Load Circuit**

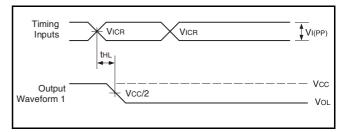

Voltage and Current Waveforms Inputs Active and Inactive Times

**Voltage Waveforms - Pulse Duration**

**Voltage Waveforms - Propagation Delay Times**

**Voltage Waveforms - Propagation Delay Times**

#### NOTES:

1. CL includes probe and jig capacitance.

2. IDD tested with clock and data inputs held at VDD or GND, and  $\mbox{Io}=0\mbox{mA}$

3. All input pulses are supplied by generators having the following characteristics: PRR  $\leq$ 10MHz, Zo = 50 $\Omega$ , input slew rate = 1 V/ns ±20% (unless otherwise specified).

4. The outputs are measured one at a time with one transition per measurement.

5. VTT = VREF = VDD/2

6. VIH = VREF + 250mV (AC voltage levels) for differential inputs. VIH = VDD for LVCMOS input.

7. VIL = VREF - 250mV (AC voltage levels) for differential inputs.

- $\mathsf{VIL}=\mathsf{GND} \text{ for } \mathsf{LVCMOS} \text{ input}.$

- 8. VID = 600mV.

- 9. TPLH and TPHL are the same as TPDM.

## Test Circuits and Waveforms (VDD = 1.8V ± 0.1V)

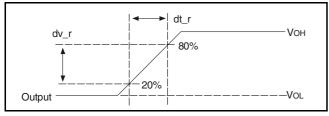

Load Circuit: High-to-Low Slew-Rate Adjustment

Voltage Waveforms: High-to-Low Slew-Rate Adjustment

Load Circuit: Low-to-High Slew-Rate Adjustment

Voltage Waveforms: Low-to-High Slew-Rate Adjustment

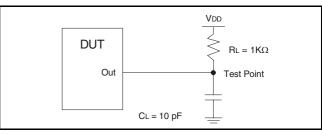

#### NOTES:

1. CL includes probe and jig capacitance.

2. All input pulses are supplied by generators having the following characteristics: PRR  $\leq$ 10MHz, Zo = 50 $\Omega$ , input slew rate = 1 V/ns ±20% (unless otherwise specified).

#### Load Circuit: Error Output Measurements

Voltage Waveforms: Open Drain Output Low-to-High Transition Time (with respect to RESET input)

Voltage Waveforms: Open Drain Output High-to-Low Transition Time (with respect to clock inputs)

Voltage Waveforms: Open Drain Output Low-to-High Transition Time (with respect to clock inputs)

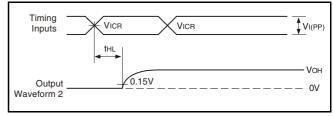

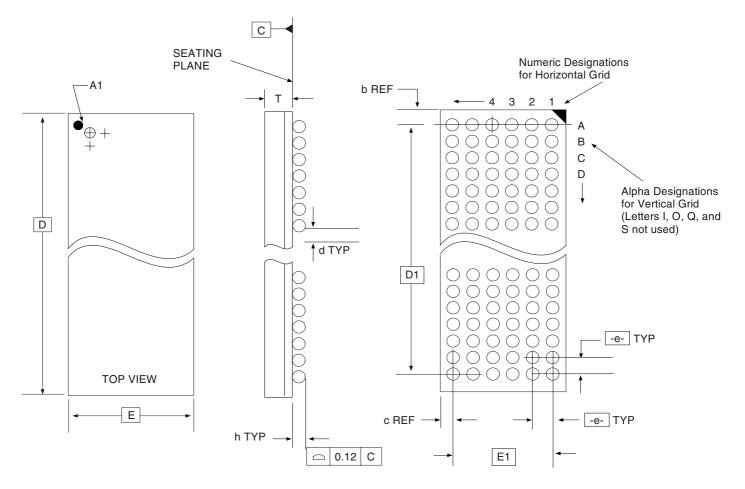

## Package Outline and Package Dimensions - BGA

Package dimensions are kept current with JEDEC Publication No. 95

#### ALL DIMENSIONS IN MILLIMETERS

|           |          | Т         |          | BALL GRID |      | d     | h         |           | REF. DIMS |          | DIMS  |       |     |

|-----------|----------|-----------|----------|-----------|------|-------|-----------|-----------|-----------|----------|-------|-------|-----|

| D         | E        | Min/Max   | е        | Horiz     | Vert | Total | Min/Max   | Min/Max   | D1        | E1       | b     | с     |     |

| 15.00 Bsc | 6.00 Bsc | 0.94/1.20 | 0.65 Bsc | 8         | 22   | 176   | 0.35/0.45 | 0.25/0.35 | 13.65 Bsc | 4.55 Bsc | 0.675 | 0.725 | *** |

NOTE: Ball grid total indicates maximum ball count for package. Lesser quantity may be used.

\* Source Ref.: JEDEC Publication 95, MO-205\*, MO-255\*\*, MO-246\*\*\*

10-0055

#### **COMMERCIAL TEMPERATURE GRADE**

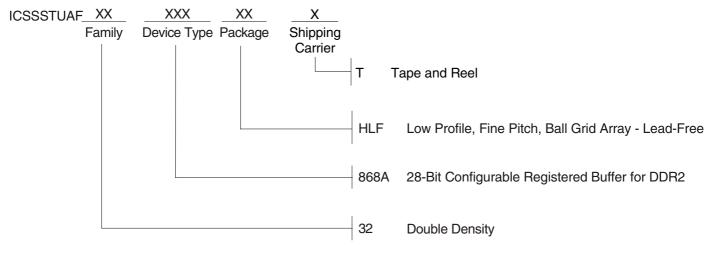

### **Ordering Information**

COMMERCIAL TEMPERATURE GRADE

### Innovate with IDT and accelerate your future networks. Contact:

## www.IDT.com

#### For Sales

800-345-7015 408-284-8200 Fax: 408-284-2775

#### **Corporate Headquarters**

Integrated Device Technology, Inc. 6024 Silver Creek Valley Road San Jose, CA 95138 United States 800 345 7015 +408 284 8200 (outside U.S.)

#### Asia Pacific and Japan

Integrated Device Technology Singapore (1997) Pte. Ltd. Reg. No. 199707558G 435 Orchard Road #20-03 Wisma Atria Singapore 238877 +65 6 887 5505

#### Europe

IDT Europe, Limited Prime House Barnett Wood Lane Leatherhead, Surrey United Kingdom KT22 7DE +44 1372 363 339

© 2006 Integrated Device Technology, Inc. All rights reserved. Product specifications subject to change without notice. IDT and the IDT logo are trademarks of Integrated Device Technology, Inc. Accelerated Thinking is a service mark of Integrated Device Technology, Inc. All other brands, product names and marks are or may be trademarks or registered trademarks used to identify products or services of their respective owners. Printed in USA